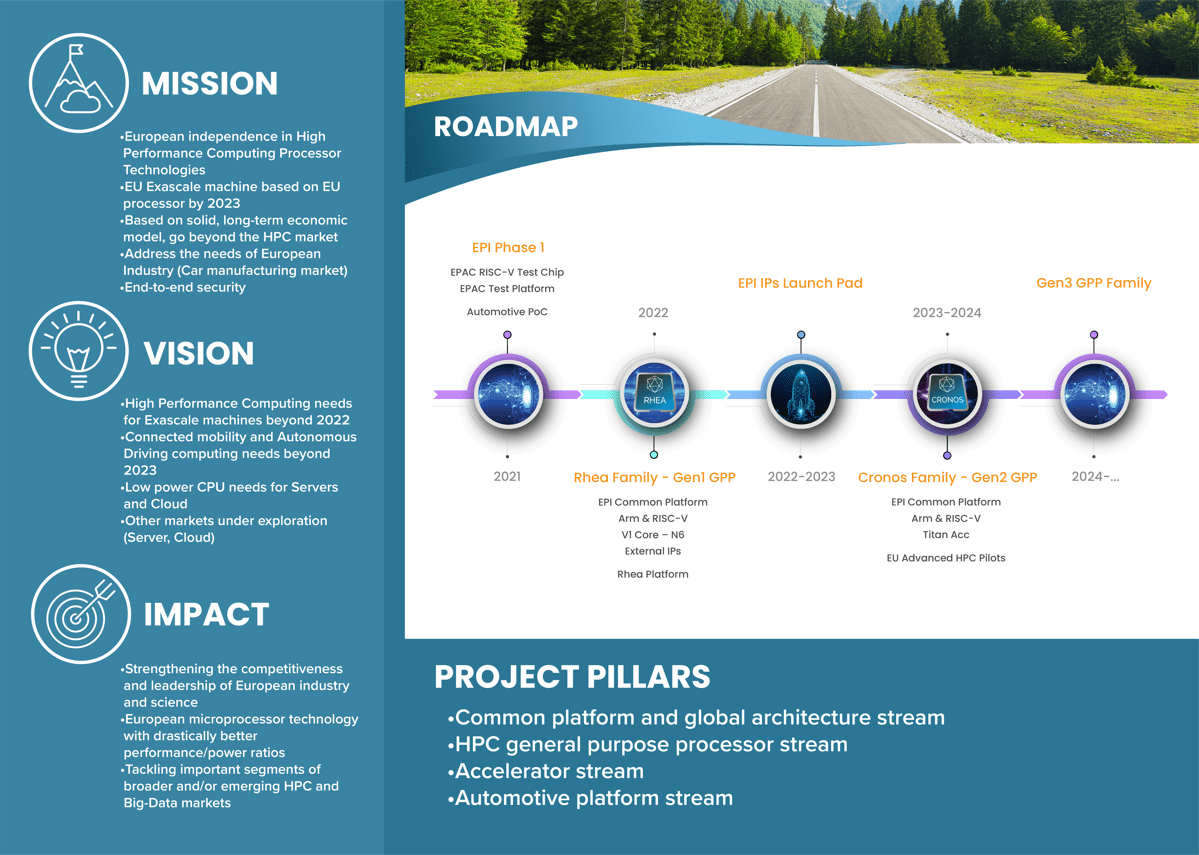

Het European Processor Initiative (EIP), een door de EU gesteund pan-Europees initiatief voor het ontwikkelen van eigen Europese processors, heeft de eerste fase afgesloten. In deze fase zijn onder meer de op Arm gebaseerde Rhea-processor, securitytechnologie voor HPC- en edge-processors en een proof-of-concept voor de European Processor Accelerator (EPAC) test chip ontwikkeld.

Europa wil al langere tijd een eigen processor -en daarbij horende industrie- ontwikkelen, zodat de regio minder afhankelijk is van processors uit andere wereldregio’s. Hiervoor hebben 28 Europese bedrijven en organisaties uit tien landen het European Processor Initiative (EIP)-consortium opgericht. Dit consortium wordt daarnaast ondersteund door de Europese Unie (EU).

Onlangs maakte het consortium bekend zijn eerste ontwikkelfase te hebben afgerond. Op basis van een budget van 79 miljoen euro werkten diverse Europese bedrijven en startups aan de ontwikkeling van eigen processortechnologie.

Resultaten eerste ontwikkelfase

Belangrijke resultaten uit deze fase zijn onder meer de introductie van de op Arm Neoverse V1 gebaseerde Rhea-processor van SiPearl in samenwerking met Atos. Hoewel de technologie van Arm uit het Verenigd Koninkrijk afkomstig is, beschikt deze processor ook over 29 als controllers werkende open-source RISC-V cores. Het gebruik van open-sourcetechnologie vormt een belangrijk onderdeel van het pan-Europese processorinitiatief. In 2023 moet deze ‘Europese’ processor worden uitgerold in supercomputeromgevingen.

Een ander resultaat van het EIP-project is het ontwikkelen van securitytechnologie voor HPC- en edge computers. Hiervoor zijn nu onder meer zogenoemde ‘crypto tiles’ ontwikkeld. Deze technologie moet integreren met andere open-source processoroplossingen en -toepassingen.

Overige oplossingen

Verder is nog de European Processor Accelerator (EPAC) test chip proof of concept in de eerste fase van het EIP-initiatief ontwikkeld. Het Barcelona Supercomputing Center en de Universiteit van Zagreb (Kroatië) ontwikkelden hiervoor onder meer zogenoemde vector processing units voor rekenkracht met hoge prestatie en een laag energieverbruik. Deze oplossing is daarbij gebaseerd op de Avispado RISC-V core van Semidynamics uit Barcelona.

Dit project leverde ook een proof of concept op voor ingebouwd compute-platform, in combinatie met een SDK, voor de autoindustrie.

Fase 2 van start in 2022

De tweede fase van het EIP moet in 2022 van start gaan. In deze fase wil het consortium zich specifiek gaan richten op het in productie brengen van de in fase 1 ontwikkelde processors.