De Taiwanese chipfabrikant TSMC werkt met Google en AMD aan een nieuwe techniek om 3d-gestapelde chips te maken. Door verschillende onderdelen van een chip bovenop elkaar te verpakken, moeten de chips compacter en efficiënter worden.

Het gerucht over de samenwerking komt van Nikkei Asia. De krant schrijft dat, nu Moore’s Law steeds lastiger wordt om bij te benen, de bedrijven kijken naar andere manieren dan procesverkleining om te ontwikkeling op gang te houden.

Andere manier van verpakking

Met de nieuwe ontwikkelingen richten de bedrijven hun pijlen op de manier dat de chips in een behuizing worden verpakt voordat ze ze op een printplaat worden geplaatst. Deze stap stond volgens Nikkei niet bekend als erg ingewikkeld zijnde, maar klaarblijkelijk is er prestatiewinst te behalen door dit anders aan te pakken.

Stapelen

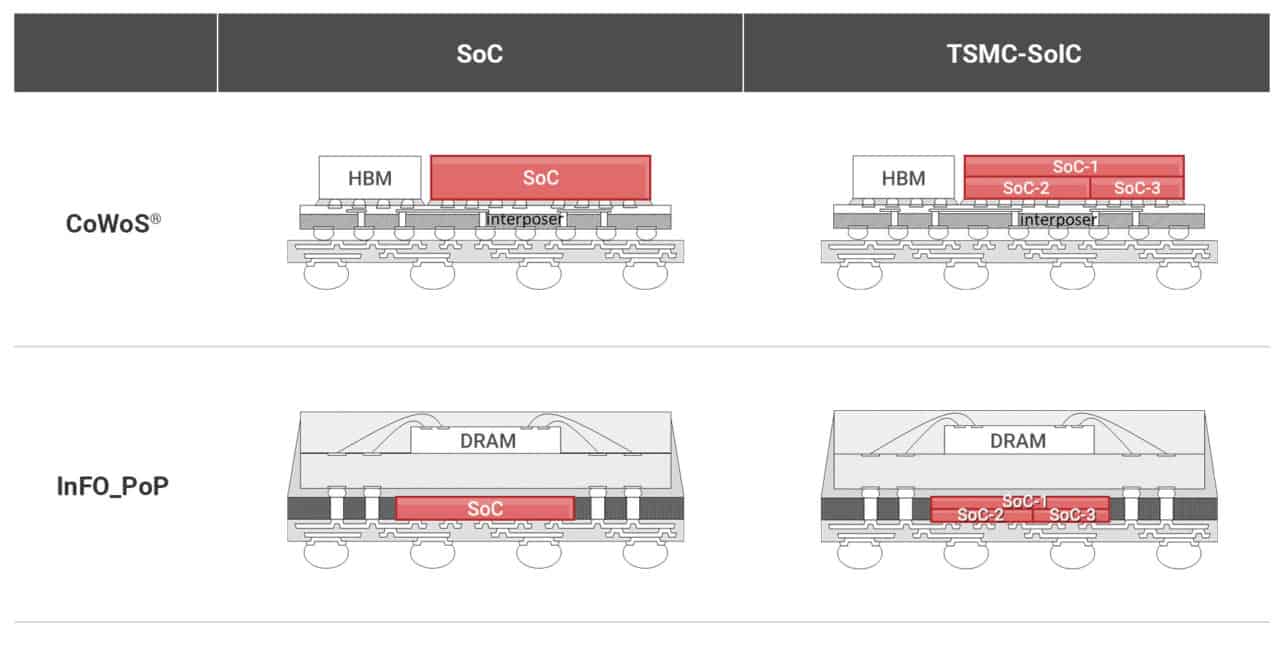

Het plan is om verschillende soorten chips, zoals de processor, het geheugen en de sensors bovenop elkaar te stapelen. Deze onderdelen worden al vaker in een enkele chip geïntegreerd, maar zijn in de meeste gevallen naast elkaar gepositioneerd. Met deze nieuwe aanpak moeten de chips kleiner, krachtiger en efficiënter worden.

2022

TSMC noemt de nieuwe 3d-stapeltechniek SoIC, wat staat voor System on Integrated Chips. De eerste klant voor de techniek is AMD, vertellen bronnen aan Nikkei. Hiervoor bouwt TSMC een fabriek in de Taiwanese stad Miaoli. De fabriek zou in 2022 gereed moeten zijn.

Tip: TSMC versnelt productieproces 5 nanometer-chip vanwege 5G introductie