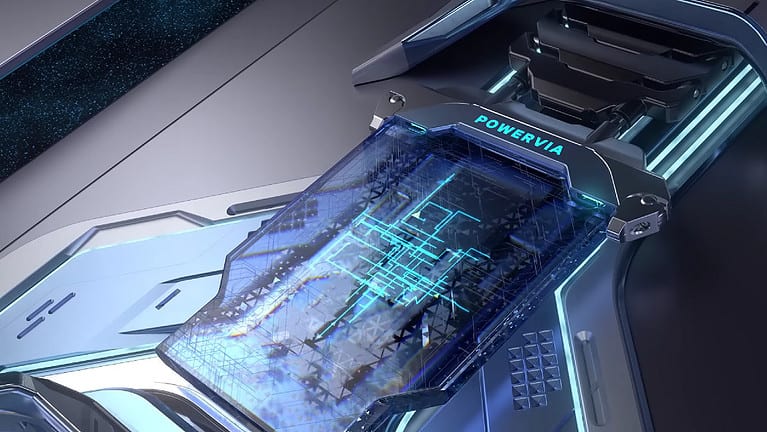

Intel pocht met de voortgang die het heeft geboekt met de eigen PowerVia-technologie. Het zou de eerste chipmaker zijn die een productiewaardige testchip met backside power delivery heeft gecreëerd. Hierdoor zou het twee jaar vooruitlopen op de concurrentie.

De Blue Sky Creek-chip bevat 8 E-cores en draait op 3 GHz. Het unieke aan deze processor is dat het niet meer de traditionele opbouw heeft van huidige CPU’s. Deze gaat uit van een opbouw die vanaf de onderkant bekeken van klein naar groot loopt: transistoren onderaan, interconnects erboven en de stroomtoevoer vanaf de bovenkant. Echter ontstaan bij deze opbouw bottlenecks op het gebied van interconnect-snelheden en de stabiliteit van stroomtoevoer. Dit zou met backside power delivery verleden tijd moeten zijn.

Van nanometer naar Ångström

Wie de ontwikkeling van processortechnologie volgt, weet dat we de afgelopen decennia steeds kleinere processen voorbij hebben zien komen. Chipfabrikanten beconcurreren elkaar continu om meer vermogen op een kleiner stukje silicium te krijgen. In deze strijd leek Intel achterop te raken, waarbij het op de 14 nanometer-naamgeving bleef steken. Dit terwijl AMD bijvoorbeeld Ryzen-chips liet bakken op TSMC-processen van 7 en 5 nanometer, bijvoorbeeld. Echter is dit eerder een situatie waarin we het over andere technologieën hebben. Net als dat klokfrequentie en het aantal cores niet per se het hele verhaal vertellen, zijn deze processen niet direct vergelijkbaar.

Intel stelt nu dat het daadwerkelijk voorop is gaan liggen in de strijd om kleinere processen, in navolging van de “five nodes in four years”-ambitie die Intel-CEO Pat Gelsinger in 2021 uitsprak. PowerVia-tech bevindt zich op 20 Ångström, oftewel 2 nanometer. Volgens VP of technology bij Intel Ben Sell is de doorbraak een belangrijke mijlpaal. Door de proefchip is Intel “een proces vóór op onze concurrentie bij het op de markt brengen van backside power delivery.” PowerVia zou de kracht achter de Arrow Lake-generatie van Intel moeten worden, dat in de eerste helft van 2024 gepland is.

Voordelen

Concreet zou de testchip een aardig aantal verbeteringen teweeg moeten brengen door de architectonische wijziging. Zo zou er meer ruimte zijn voor de interconnect-laag door het verdwijnen van de stroomtoevoer aan de voorkant. Er zou 30 procent minder ‘voltage droop’ zijn en een voordeel van 6 procent qua frequentie. Puur qua uiterlijk verandert er weinig en er zou zelfs geen probleem met de opbouw van hitte zijn, ondanks dat deze opbouw compleet nieuw is voor productie-chips.